Die Urheberrechte an diesem Handbuch liegen bei Shenzhen Thinkcore Technology Co., Ltd. und alle Rechte sind vorbehalten. Unternehmen oder Einzelpersonen dürfen dieses Handbuch weder ganz noch teilweise extrahieren, und Zuwiderhandlungen werden strafrechtlich verfolgt.

Die Handbücher der zum Verkauf stehenden Entwicklungsplattform werden von Zeit zu Zeit aktualisiert. Bitte laden Sie das neueste Handbuch von der Website www.think-core.com herunter oder wenden Sie sich an unseren Vertriebsmitarbeiter des Unternehmens, es erfolgt keine weitere Benachrichtigung.

|

Ausführung |

Datum |

Autor |

Beschreibung |

|

Rev.01 |

04.08.2022 |

|

Revision |

TC-RK3568 Stanzloch-Entwicklungsplatine Kurz

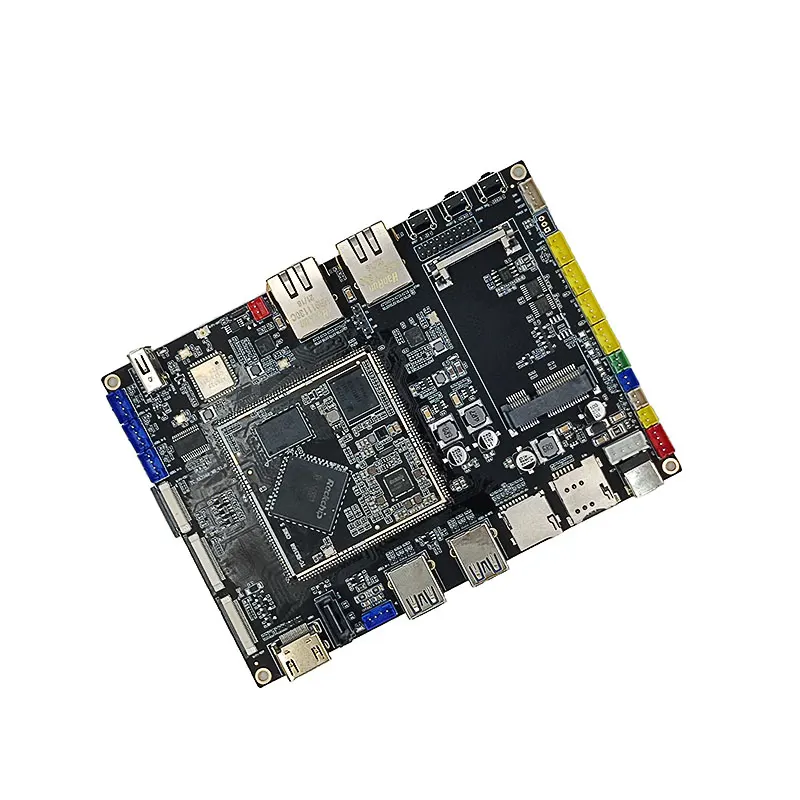

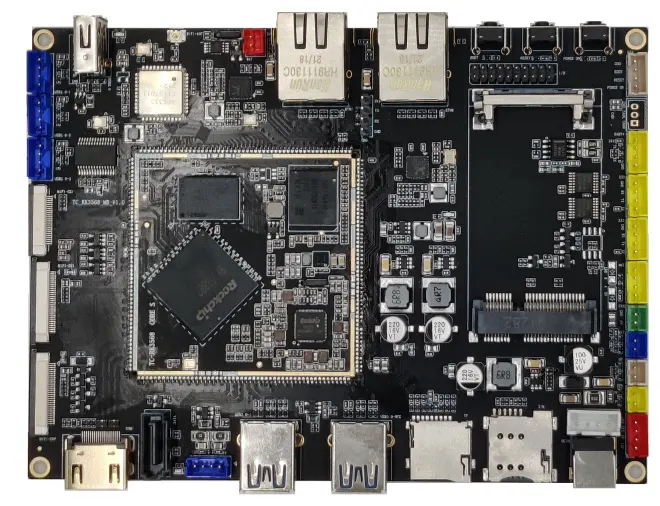

TC-RK3568 Stamp Hole Development Board enthält TC-RK3568 Stamp Hole SOM und Trägerplatine.

Das TC-RK3568 Stamp Hole-System auf dem Modul ist mit dem Rockchip 64-Bit-Prozessor RK3568 ausgestattet, der mit einer Dual-Core-GPU und einer Hochleistungs-NPU konfiguriert ist.

RK3568, der Quad-Core-64-Bit-Cortex-A55-Prozessor mit 22-nm-Lithographieprozess, hat eine Frequenz von bis zu 2,0 GHz und bietet eine effiziente und stabile Leistung für die Datenverarbeitung von Back-End-Geräten. Es gibt eine Vielzahl von Lagermöglichkeiten, die es Kunden ermöglichen, die Forschung und Produktion von Produkten schnell umzusetzen. Es unterstützt bis zu 8 GB RAM mit bis zu 32 Bit Breite und einer Frequenz von bis zu 1600 MHz. Es unterstützt All-Data-Link-ECC, wodurch Daten sicherer und zuverlässiger werden und die Anforderungen für die Ausführung von Produktanwendungen mit großem Speicher erfüllt werden. Es ist mit einer Dual-Core-GPU, einer Hochleistungs-VPU und einer hocheffizienten NPU integriert. Die GPU unterstützt OpenGL ES3.2/2.0/1.1, Vulkan1.1. Die VPU kann 4K 60fps H.265/H.264/VP9-Videodekodierung und 1080P 100fps H.265/H.264-Videokodierung erreichen. Die NPU unterstützt das Umschalten von Mainstream-Frameworks wie Caffe/TensorFlow mit einem Klick.

Mit MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, EDP-Videoschnittstellen kann es bis zu drei Bildschirmausgaben mit unterschiedlicher Anzeige unterstützen. Der eingebaute 8M ISP unterstützt Dual-Kameras und HDR. Die Videoeingangsschnittstelle kann an eine externe Kamera oder mehrere Kameras angeschlossen werden. Es ist mit zwei adaptiven RJ45-Gigabit-Ethernet-Ports ausgestattet, über die auf interne und externe Netzwerkdaten zugegriffen und diese übertragen werden können, wodurch die Netzwerkübertragungseffizienz verbessert und die Anforderungen von Produkten mit mehreren Netzwerkports wie NVR und Industrie-Gateway erfüllt werden.

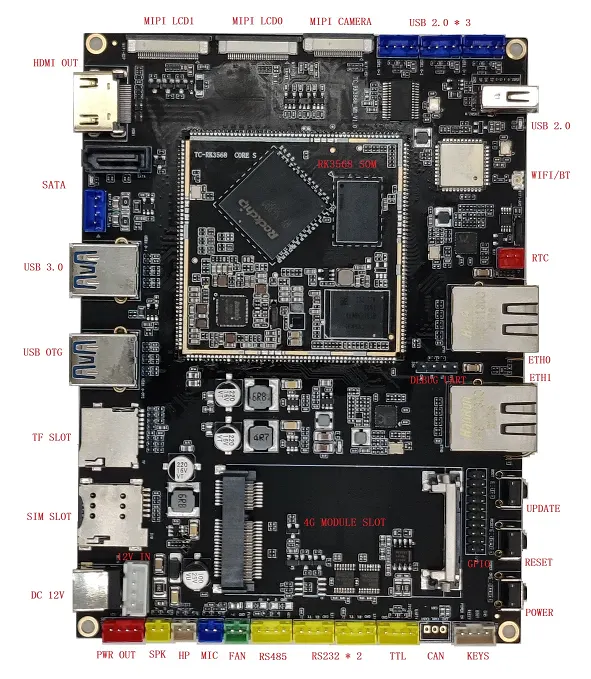

Das Trägerboard beinhaltet viele Schnittstellen, wie 4G LTE Port, USB3.0, USB2.0, PCIE, Dual Ethernet, WIFI, Bluetooth, Audio Ein- und Ausgang, HDMI Out, MIPI DSI Display, eDP Display, LVDS Display, MIPI CSI Kamera, TF-Kartensteckplatz, RS485, RS232, TTL, CAN, Stromausgang, SATA usw.

Android 11, Ubuntu 18.04 OS, Debian OS und Linux Buildroot werden unterstützt. Der stabile und zuverlässige Betrieb bietet eine sichere und stabile Systemumgebung für die Produktforschung und -produktion.

Ein vollständiges SDK, Entwicklungsdokumente, Beispiele, Technologiedokumente, Tutorials und andere Ressourcen werden den Benutzern zur Verfügung gestellt, um eine weitere Anpassung vorzunehmen.

Größe: 150 x 110 mm.

Reichhaltige Schnittstellen, können direkt in verschiedenen intelligenten Produkten verwendet werden, um die Fertigstellung von Produkten zu erleichtern.

Android 11.0, Ubuntu 18.04 OS, Debian OS und Linux Buildroot werden unterstützt.

Dieses Board kann weit verbreitet in intelligenten NVRs, Cloud-Terminals, IoT-Gateways, Industriesteuerungen, Edge-Computing, Gesichtserkennungstoren, NASs, Fahrzeug-Mittelkonsolen usw. verwendet werden.

|

Spezifikationen |

|

|

Zentralprozessor |

RockChip RK3568, Quad-Core 64-Bit Cortex-A55, 22-nm-Lithographieprozess, Frequenz bis zu 2,0 GHz |

|

Grafikkarte |

ARM G52 2EE Unterstützt OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Eingebettete Hochleistungs-2D-Beschleunigungshardware |

|

NPU |

0.8Tops@INT8, integrierter Hochleistungs-KI-Beschleuniger RKNN NPU Unterstützt das Umschalten von Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet mit einem Klick |

|

VPU |

Unterstützt 4K 60 fps H.265/H.264/VP9-Videodekodierung Unterstützt 1080P 100fps H.265/H.264-Videocodierung Unterstützt 8M ISP, unterstützt HDR |

|

RAM |

2GB/4GB/8GB |

|

Lagerung |

8 GB/16 GB/32 GB/64 GB/128 GB eMMC Unterstützt SATA 3.0 x 1 (Erweitern mit 2,5-Zoll-SSD/HDD) Unterstützt TF-Kartensteckplatz x1 (Erweitern mit TF-Karte) |

|

Systembetriebssystem |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Hardwarefunktionen |

|

|

Anzeige |

1 * HDMI2.0, unterstützt 4K@60fps-Ausgabe 1 * MIPI DSI, unterstützt eine Ausgabe von 1920 * 1080 bei 60 fps 1 * LVDS, unterstützt 1920*1080@60fps Ausgabe 1 * eDP1.3, unterstützt 2560x1600@60fps Ausgabe |

|

Ethernet |

Unterstützt zwei Gigabit-Ethernet-Ports (1000 Mbit/s) |

|

W-lan |

Mini PCIe zum Anschluss von 4G LTE Unterstützt WiFi 6 (802.11 AX) Unterstützt BT5.0 |

|

PCIE3.0 |

Unterstützt PCE3.0-Schnittstelle |

|

Audio |

1 * HDMI-Audioausgang 1 * Lautsprecherausgang 1 * Kopfhörerausgang 1 * Onboard-Audioeingang für Mikrofon |

|

Kamera |

Unterstützt 1-Kanal-MIPI-CSI-Kameraschnittstelle Unterstützt HDR, das Bild bleibt bei Gegenlicht oder starken Lichtverhältnissen klar

|

|

USB |

1 * USB3.0-Host, 4 * USB 2.0-Host, 1 * USB3.0 OTG |

|

SATA |

1 * SATA, 6,0 Gbit/s |

|

Seriell |

1 * TTL, 2 * RS232, 1 * RS485 |

|

KANN |

Unterstützt CAN2.0B, unterstützt 1 Mbit/s, 8 Mbit/s |

|

TF-Karte |

1 * TF-Kartensteckplatz |

|

Andere |

GPIO und ADC |

|

Größe |

150mm*110mm |

|

|

|

|

Eingangsspannung |

12V/3A |

|

Lagertemperatur

|

-30 ~ 80 ℃ |

|

Betriebstemperatur |

-20~60 ℃ |

|

Lagerfeuchtigkeit |

10%~80% |

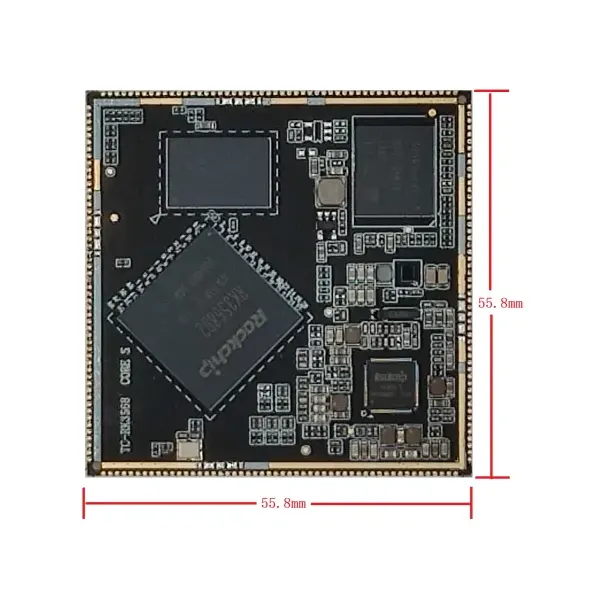

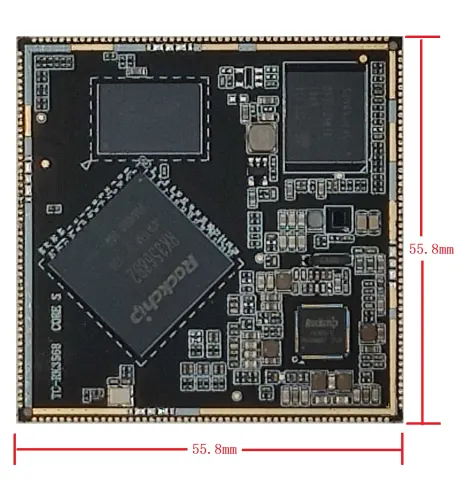

SOM-Front

|

STIFT |

Kernplatinen-Pin-Definition |

Standardfunktion |

Beschreibung der Standardfunktion |

IO-Leistung |

Pad-Typ IO Pull |

|

1 |

VCC3V3_SYS |

3,3-V-Systemstromversorgung |

Eingangsspannung 3,3 V |

|

- |

|

2 |

VCC3V3_SYS |

3,3-V-Systemstromversorgung |

Eingangsspannung 3,3 V |

|

- |

|

3 |

Masse |

Masse |

Masse |

|

- |

|

4 |

Masse |

Masse |

Masse |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

SDMMC0 erkennt Eingang |

3,3 V |

E/A AUF |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

SDMMC0-Datenport |

3,3 V |

E/A AUF

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

SDMMC0-Datenport |

3,3 V |

E/A AUF

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

SDMMC0-Datenport |

3,3 V |

E/A AUF

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

SDMMC0-Datenport |

3,3 V |

E/A AUF

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

SDMMC0-Befehlsausgabe |

3,3 V |

E/A AUF

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

SDMMC0-Taktausgang

|

3,3 V |

E/A AUS |

|

12 |

RESETN |

NPOR_U |

Signalerkennung zurücksetzen |

3,3 V |

- |

|

13 |

RK809_PWRON |

Ein |

Signaleingang einschalten, Power-Taste für externe Verbindung, aktiv niedrig |

|

- |

|

14 |

ERHOLUNG |

SARADC_VIN0 |

AD-Tastatureingabe |

1,8 V |

- |

|

15 |

EXT_EN |

EXT_EN |

PMIC-Stromversorgung aktivieren |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Kopfhörer direkt raus |

3,3 V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Kopfhörer weggelassen |

3,3 V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

Aussprechen |

5V/0,6W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

Aussprechen- |

5V/0,6W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3,3 V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3,3 V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Kopfhörer erkennen |

3,3 V |

E/A AUS |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3,3 V |

E/A AUS |

|

24 |

VCC3V3_SD |

3,3-V-Netzteil |

Ausgangsspannung 3,3 V für SD-Karte, Nennausgangsstrom 2 A |

|

- |

|

25 |

VCC_3V3 |

3,3-V-Netzteil |

Ausgangsspannung 3,3 V, Nennausgangsstrom 2 A |

|

- |

|

26 |

VCC_1V8 |

1,8 V Netzteil |

Ausgangsspannung 1,8 V, Nennausgangsstrom 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3,3 V |

IO UNTEN |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3,3 V |

IO UNTEN |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3,3 V |

IO UNTEN |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3,3 V |

IO UNTEN |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0-Sendedaten |

1,8 V |

E/A AUF |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0-Sendedaten |

1,8 V |

E/A AUF |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0-Sendedaten |

1,8 V |

E/A AUF |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0-Sendedaten |

1,8 V |

E/A AUF |

|

35 |

GMAC0_TXEN |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

GMAC0-Sendefreigabe |

1,8 V |

E/A AUF |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

GMAC0-Sendetakt |

1,8 V |

E/A AUS |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 empfängt Daten |

1,8 V |

E/A AUF |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 empfängt Daten |

1,8 V |

E/A AUS |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 empfängt Daten |

1,8 V |

E/A AUF |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 empfängt Daten |

1,8 V |

E/A AUF |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

GMAC0 RX-Daten gültiges Signal |

1,8 V |

E/A AUS |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

GMAC0-Empfangsuhr |

1,8 V |

E/A AUF |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25MHz CPU zu PHY, Standard NC |

1,8 V |

E/A AUS |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

GMAC0 externe Uhr |

1,8 V |

E/A AUS |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

MAC0-Verwaltungsuhr |

1,8 V |

E/A AUS |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

MAC0-Verwaltungsbefehl und -daten |

1,8 V |

E/A AUS |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3,3 V |

IO UNTEN |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3,3 V |

E/A AUS |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, aktiv niedrig |

1,8 V |

E/A AUS |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

Serielle I2C-Schnittstelle 5 |

3,3 V |

E/A AUS |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

Serielle I2C-Schnittstelle 5 |

3,3 V |

E/A AUS |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3,3 V |

E/A AUS |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

CAN-Daten übertragen |

3,3 V |

E/A AUS |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

CAN-Daten empfangen |

3,3 V |

E/A AUS |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

Serielle UART-Schnittstelle |

3,3 V |

E/A AUF |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Übertragen von Daten der seriellen UART-Schnittstelle zum Debuggen |

3,3 V |

E/A AUF |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

UART Searial Port Daten empfangen |

3,3 V |

E/A AUS |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

UART-Serial-Port-Datenübertragung |

3,3 V |

E/A AUS |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

UART-Serial-Port-Datenübertragung |

3,3 V |

E/A AUS |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

UART Searial Port Daten empfangen |

3,3 V |

E/A AUS |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

UART Searial Port Daten empfangen |

3,3 V |

E/A AUS |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

UART-Serial-Port-Datenübertragung |

3,3 V |

E/A AUS |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

UART Searial Port Daten empfangen |

3,3 V |

E/A AUS |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

UART-Serial-Port-Datenübertragung |

3,3 V |

E/A AUS |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

RS485-Datenrichtung |

3,3 V |

E/A AUS |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3,3 V |

E/A AUF |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3,3 V |

E/A AUS |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDDMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3,3 V |

E/A AUS |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDDMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3,3 V |

E/A AUS |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3,3 V |

E/A AUS |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3,3 V |

E/A AUS |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3,3 V |

E/A AUS |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDDMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3,3 V |

E/A AUS |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Einschalten des Bluetooth-Moduls |

3,3 V |

E/A AUS |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

UART Searial Port Daten empfangen |

1,8V |

E/A AUS |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

UART-Serial-Port-Datenübertragung |

1,8 V |

E/A AUS |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1,8 V |

E/A AUS |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1,8 V |

E/A AUS |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

WIFI_REG aktivieren |

1,8 V |

E/A AUS |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

WIFI Wake-Up-Host |

1,8 V |

E/A AUS |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

SDMMC2-Uhr |

1,8 V |

E/A AUS |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

SDMMC2-Befehl |

1,8 V |

E/A AUS |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

SDMMC2-Daten |

1,8 V |

E/A AUS |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

SDMMC2-Daten |

1,8 V |

E/A AUS |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

SDMMC2-Daten |

1,8 V |

E/A AUS |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

SDMMC2-Daten |

1,8 V |

E/A AUS |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3,3 V |

E/A AUS |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3,3 V |

E/A AUS |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

GMAC1-Verwaltungsbefehl und -daten |

1,8 V |

E/A AUS |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

GMAC1-Verwaltungsuhr |

1,8 V |

E/A AUS |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDCLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

GMAC1 externe Uhr |

1,8 V |

E/A AUS |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

ETH1 Taktausgang |

1,8 V |

E/A AUS |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

GMAC1-Empfangsuhr |

1,8 V |

E/A AUS |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

GMAC1 RX-Daten gültiges Signal |

1,8 V |

E/A AUS |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 empfängt Daten |

1,8 V |

E/A AUS |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 empfängt Daten |

1,8 V |

E/A AUS |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 empfängt Daten |

1,8 V |

E/A AUS |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 empfängt Daten |

1,8 V |

E/A AUS |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

GMAC1-Sendetakt |

1,8 V |

E/A AUS |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

GMAC1-Sendefreigabe |

1,8 V |

E/A AUS |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1-Sendedaten |

1,8 V |

E/A AUS |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1-Sendedaten |

1,8 V |

E/A AUS |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1-Sendedaten |

1,8 V |

E/A AUS |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1-Sendedaten |

1,8 V |

E/A AUS |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Zurücksetzen des Touchpanels |

3,3 V |

E/A AUF

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Touchpanel unterbricht Dateneingabe |

3,3 V |

E/A AUF |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

Serielle I2C-Schnittstelle 1 |

3,3 V |

E/A AUF |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

Serielle I2C-Schnittstelle 1 |

3,3 V |

E/A AUF |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

Serielle I2C-Schnittstelle 3 |

3,3 V |

E/A AUF |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

Serielle I2C-Schnittstelle 3 |

3,3 V |

E/A AUF |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

Serielle I2C-Schnittstelle 2 |

1,8 V |

E/A AUS |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

Serielle I2C-Schnittstelle 2 |

1,8 V |

E/A AUS |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Kamera 1 ausschalten |

3,3 V |

E/A AUS |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Kamera1 zurückgesetzt |

3,3 V |

E/A AUS |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Kamera0 zurückgesetzt |

3,3 V |

E/A AUS |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Kamera0 ausschalten |

3,3 V |

E/A AUS |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3,3 V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3,3 V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3,3 V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3,3 V |

- |

|

121 |

REFCLK_OUT |

REFCLK_OUT/GPIO0_A0_d |

Taktausgang für Kamera |

3,3 V |

E/A AUS |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

CIF-Uhr aus |

1,8 V |

E/A AUS |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1,8 V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1,8 V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1,8 V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1,8 V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1,8 V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1,8 V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1,8 V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1,8 V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1,8 V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1,8 V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1,8 V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1,8 V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

LCD-Stromversorgung aktivieren |

3,3 V |

E/A AUS |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

LCD-Hintergrundbeleuchtung PWM |

3,3 V |

E/A AUS |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

LCD-Hintergrundbeleuchtung PWM |

3,3 V |

E/A AUS |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

LCD-Stromversorgung aktivieren |

3,3 V |

E/A AUS |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1,8 V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1,8 V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1,8 V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1,8 V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1,8 V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1,8 V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1,8 V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1,8 V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1,8 V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1,8 V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT und Serienwiderstand 2.2R |

1,8 V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT und Serienwiderstand 2.2R |

1,8 V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT und Reihenwiderstand 2.2R |

1,8 V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Serielle I2C-Schnittstelle für HDMI |

3,3 V |

E/A AUF |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Serielle I2C-Schnittstelle für HDMI |

3,3 V |

E/A AUF |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3,3 V |

E/A AUF |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

HDMI_TX-Hotplug |

1,8 V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

E/A AUS |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3,3 V |

E/A AUS |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

PCIE30X2 zurückgesetzt |

3,3 V |

E/A AUS |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

PCIE30X2 Wake-Host |

3,3 V |

E/A AUS |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

PCIE-Stromversorgung aktivieren |

1,8 V |

E/A AUS |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1,8 V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1,8 V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1,8 V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1,8 V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1,8 V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1,8 V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1,8 V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1,8 V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1,8 V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1,8 V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1,8 V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1,8 V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1,8 V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1,8 V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1,8 V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1,8 V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA aktiv anzeigen |

3,3 V |

E/A AUS |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1,8 V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1,8 V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1,8 V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1,8 V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3,3 V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3,3 V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1,8 V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1,8 V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1,8 V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1,8 V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3,3 V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3,3 V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3,3 V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUS erkennen |

3,3 V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

USB-Host-Stromversorgung aktivieren |

3,3 V |

E/A AUS |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

USB-OTG-Stromversorgung aktivieren |

3,3 V |

E/A AUS |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1,8 V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1,8 V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1,8 V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1,8 V |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1,8 V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1,8 V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1,8 V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1,8 V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1,8 V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1,8 V |

- |

Die Größe beträgt 150 mm * 110 mm, 4 Schichten, 1,6 mm Dicke.

|

Beschreibung der Schnittstellen |

|

|

NEIN. |

Name |

|

ã1ã |

12-V-Gleichstromeingang/4-poliger 2,54-mm-12-V-Eingang |

|

ã2ã |

SIM-Kartensteckplatz für 4G-Modul |

|

ã3ã |

TF-Karten-Slot |

|

ã4ã |

USB-OTG |

|

ã5ã |

USB3.0-HOST |

|

ã6ã |

SATA-Daten |

|

ã7ã |

HDMI-Ausgang |

|

ã8ã |

MIPI-LCD1 |

|

ã9ã |

MIPI-LCD0 |

|

ã10ã |

MIPI-Kamera |

|

ã11ã |

USB2.0 * 3 |

|

ã12ã |

USB2.0 TypA |

|

ã13ã |

WLAN/BT (AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Schlüssel aktualisieren |

|

ã18ã |

Schlüssel zurücksetzen |

|

ã19ã |

Kraftschlüssel |

|

ã20ã |

Schlüssel (4-polig 2,0 mm) |

|

ã21ã |

KÖNNEN (3-polig 2,0 mm) |

|

ã22ã |

Uart-TTL (4-polig 2,0 mm) |

|

ã23ã |

RS232 * 2 (4-polig 2,0 mm) |

|

ã24ã |

RS485 (4-polig 2,0 mm) |

|

ã25ã |

LÜFTER (2-polig 2,0 mm) |

|

ã26ã |

Mikrofon (2-polig 2,0 mm) |

|

ã27ã |

HP (2-polig 2,0 mm) |

|

ã28ã |

SPK (2-polig 2,0 mm) |

|

ã29ã |

Stromausgang (4-polig 2,0 mm) |

|

ã30ã |

Debug-Uart (4-polig 2,0 mm) |

|

ã31ã |

GPIO(2*10pin 2,0mm) |

|

ã32ã |

4G-Modulsteckplatz (PCIE-Port) |

|

ã33ã |

RK3568 SOM |

Das Board verwendet eine 12-V-DC-Stromversorgung, die über einen 12-V-DC-Eingangsanschluss oder einen 4-poligen 2,54-mm-12-V-Eingangsanschluss angeschlossen wird.

Einzelheiten zu anderen Schnittstellen können dem schematischen Diagramm und dem Layout des Entwicklungsboards entnommen werden.

Nehmen Sie das TC-RK3568-Entwicklungsboard als Hardwareplattform, Sie könnten sich auf Power-Design, USB-Design, PCIE-Port-Design, MIPI-Display-Design, Audio-Design, Ethernet-Design, Kamera-Design und so weiter beziehen. Diese stehen Kunden offen, die sich auf unser Carrierboard-Design beziehen können.

Die Entwicklungsplattform TC-RK3568 unterstützt Android11, Linux Buildroot, Ubuntu und Debian System OS, Quellcodes sind offen. Sie können die Referenzen wie das Thinkcore TC-RK3568-Systembenutzerhandbuch lesen.